# Inline Defect Part Average Testing (I-PAT<sup>™</sup>)

David W. Price\*, Robert J. Rathert, Naema Bhatti, Kara Sherman, Doug Sutherland, Chet Lenox, and Robert Cappel

**KLA-Tencor Corporation**

April 25, 2018

\*david.w.price@kla-tencor.com

2018 Automotive Electronics Council Reliability Workshop

- 1. Introduction and Problem Statement

- 2. I-PAT Description

- 3. I-PAT Implementation Examples

#### **KLA-Tencor Overview**

Global Leader in Process Control since 1976

**17** countries

R&D investment over last 4 fiscal years

#### **KLA-Tencor Markets Served**

#### Semiconductor Manufacturing

#### **Related Nanoelectronics Industries**

4

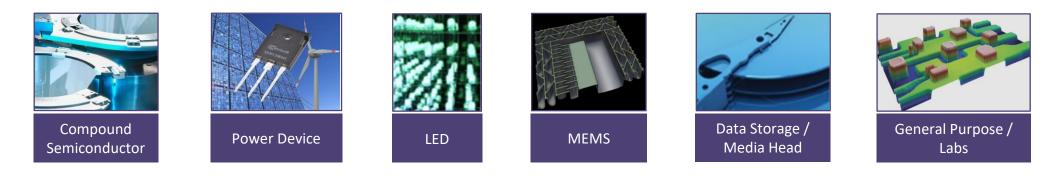

## Electronics is Already the #1 source of 0km Failures

- Shrinking Maturity Window

- Increasing Chip Content

- Increasing Quality Requirements

- Decreasing Test Coverage

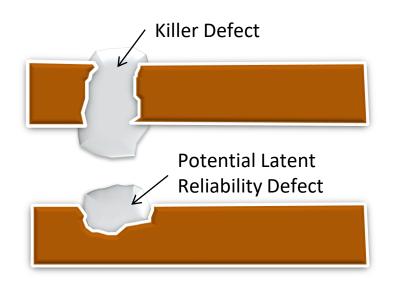

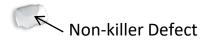

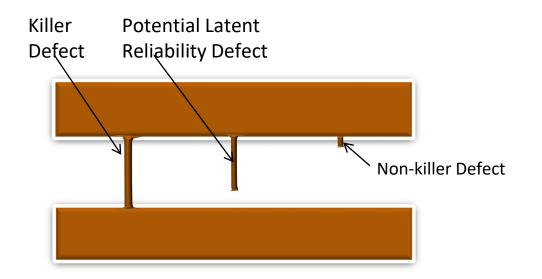

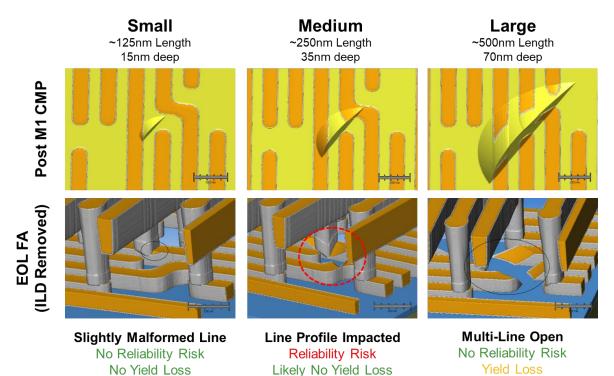

1. The defect types that impact reliability are generally the same as those that impact yield. They are distinguished primarily by size and proximity to critical design features.

6

1. The defect types that impact reliability are generally the same as those that impact yield. They are distinguished primarily by size and proximity to critical design features.

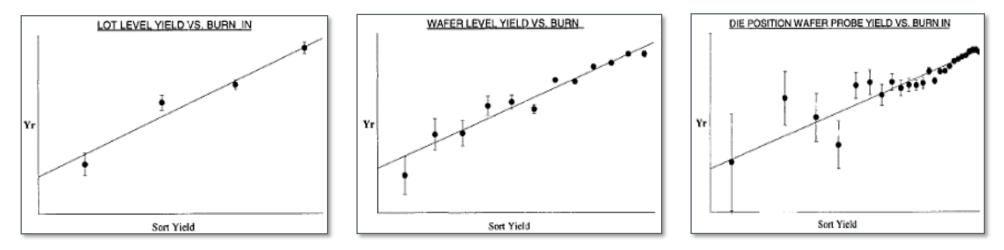

2. There is a direct correlation between yield and reliability at the lot, wafer, and die level. Total defectivity can be used as a proxy for LRD's.

Low yielding <u>lots</u> have degraded reliability

Low yielding <u>wafers</u> have degraded reliability

Low yielding <u>die locations</u> have degraded reliability

Riordan et al. (Intel) "Microprocessor Reliability Performance as a Function of Die Location for a .25um, Five Layer Metal CMOS Logic Process"

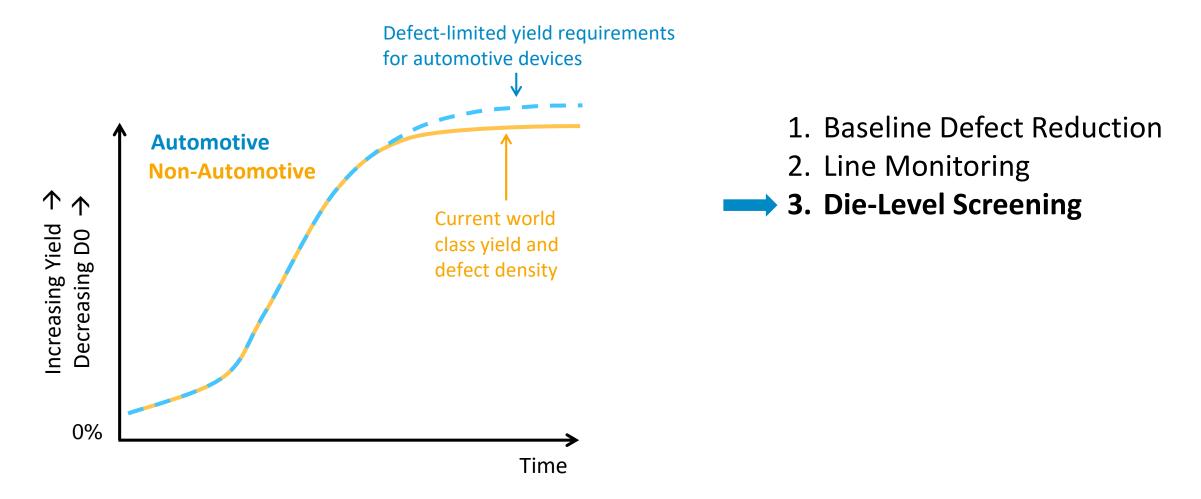

3. The best way to reduce the possibility of latent reliability defect escapes is to reduce the fab's overall level of random defectivity.

## **Die-Level Screening for Latent Reliability Defects?**

#### Rationale:

- **On-wafer random defectivity** is one of the main culprits for 0km and field failures.

- Fabs already use of inline defect inspection for yield improvement and line monitoring.

#### Challenge:

• Only a very small fraction of defects produce latent reliability failures.

Need a statistical approach that can use machine learning to improve as we improve our understanding of latent defects.

# **Presentation Outline**

1. Introduction and Problem Statement

2. I-PAT Description

3. I-PAT Implementation Examples

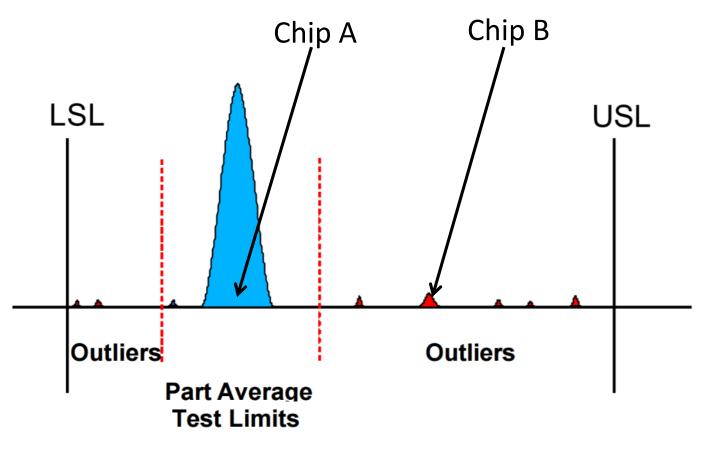

## Part Average Testing

*Is there a <u>statistical</u> difference in chip reliability between Chip A and B?*

- Statistical screening technique

- Introduced by AEC in 1997

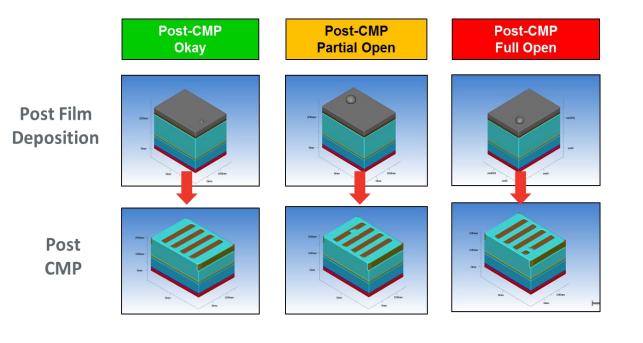

#### Inline Defect Part Average Testing (I-PAT)

*Is there a <i>statistical difference in chip reliability between Chip A and B?*

Inspection Layer 1 (LS) Inspection Layer 2 (LS) Inspection Layer 3 (macro) Inspection Layer 4 (LS) Inspection Layer 5 (BBP) Inspection Layer 6 (LS) Inspection Layer 7 (LS) Inspection Layer 8 (BBP)

**Inspection Layer N**

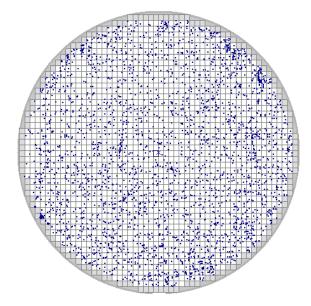

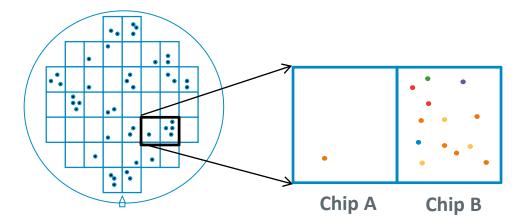

Stacked-defect die map created by adding together the defects from multiple inline inspection steps

KLA Tencor

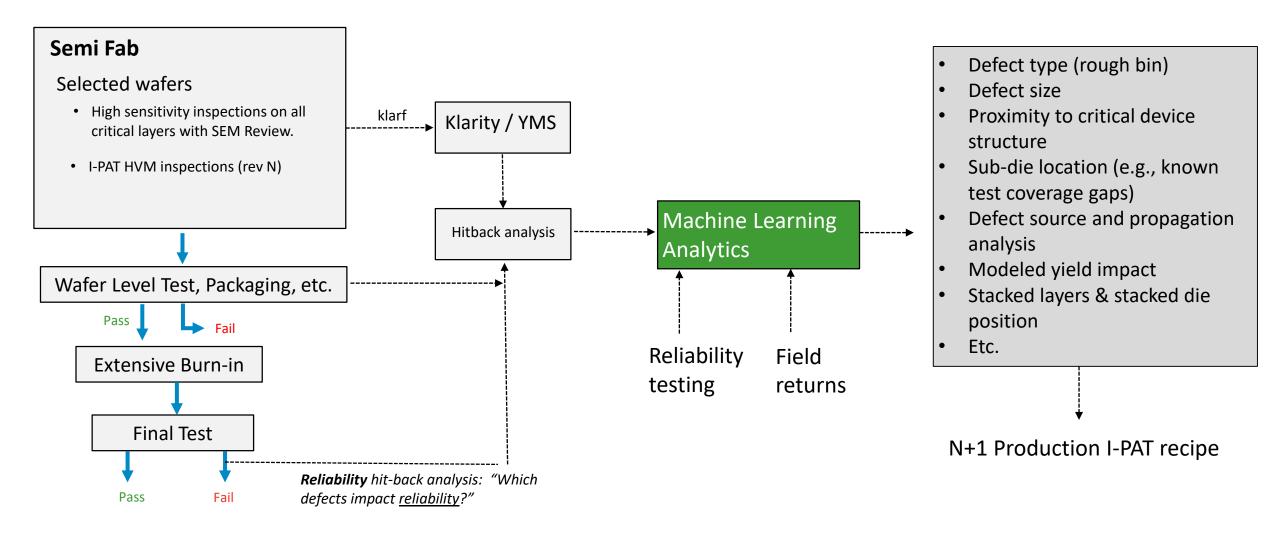

## Inline Defect Part Average Testing (I-PAT)

*I-PAT is the process of using <u>inline</u> <u>defect</u> data to <u>selectively</u> ink-off (i.e., map downgrade) die which have an elevated risk of latent reliability failures.*

#### Key Elements

- Requires 100% inspection at key steps for the product(s) being screened. Results automatically → ink and scrap.

- Leverages the observed correlation between defectivity and reliability.

- Defect attributes, statistical filters, and advanced correlation engines are employed to improve capture and reduce overkill.

# **Presentation Outline**

1. Introduction and Problem Statement

2. I-PAT Description

3. I-PAT Implementation Examples

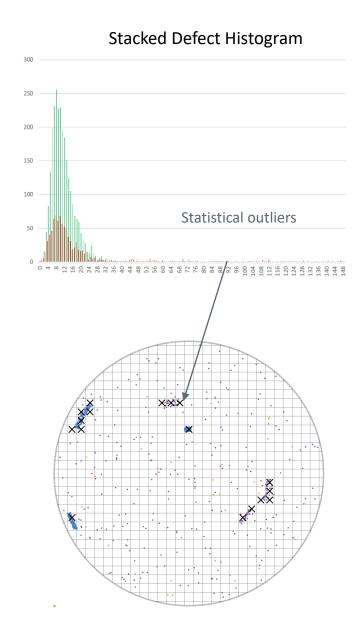

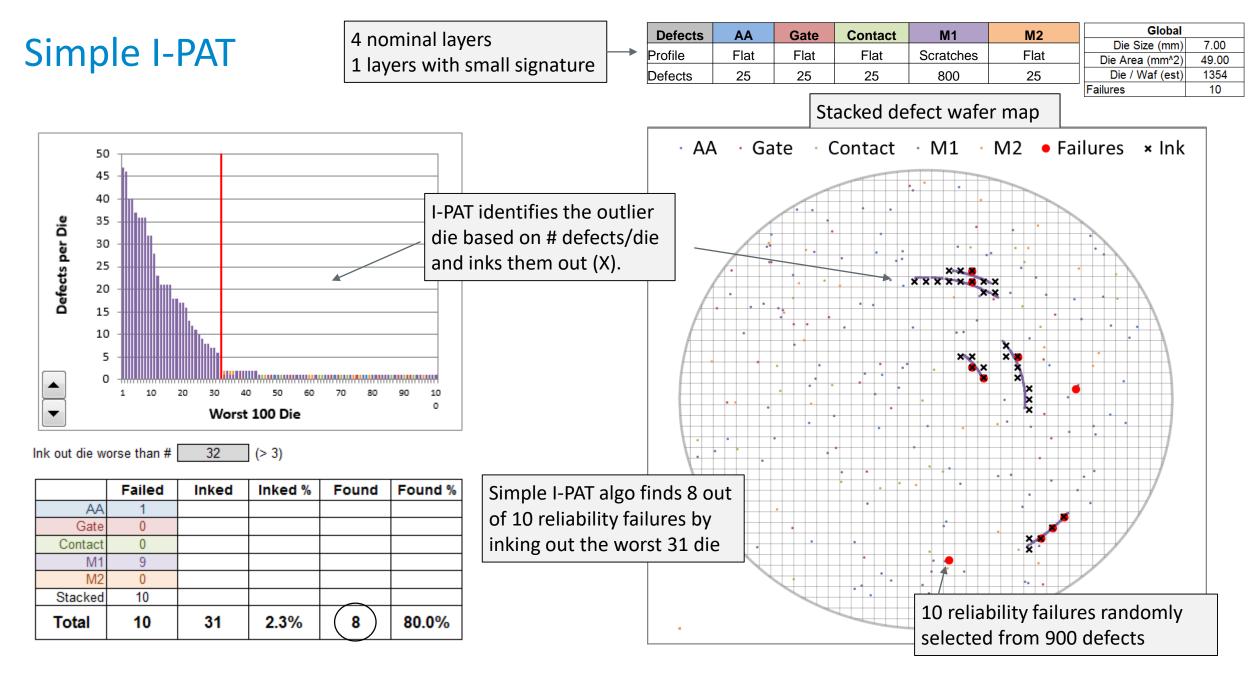

### Simple I-PAT Implementation

Predicated on the observation that the probability distribution of latent defectivity roughly follows the distribution in total defectivity

$P(LRD)_i = N_i m$

The probability of die *i* having a **\_\_** latent reliability defect

The total number of X defects in die *i*.

The ratio of latent reliability defects to total defectivity (0 < m << 1)

*Chip B has a 15x higher statistical probability of a latent reliability failure than Chip A*

KLA Tencor

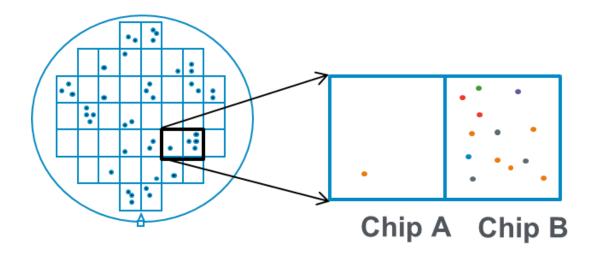

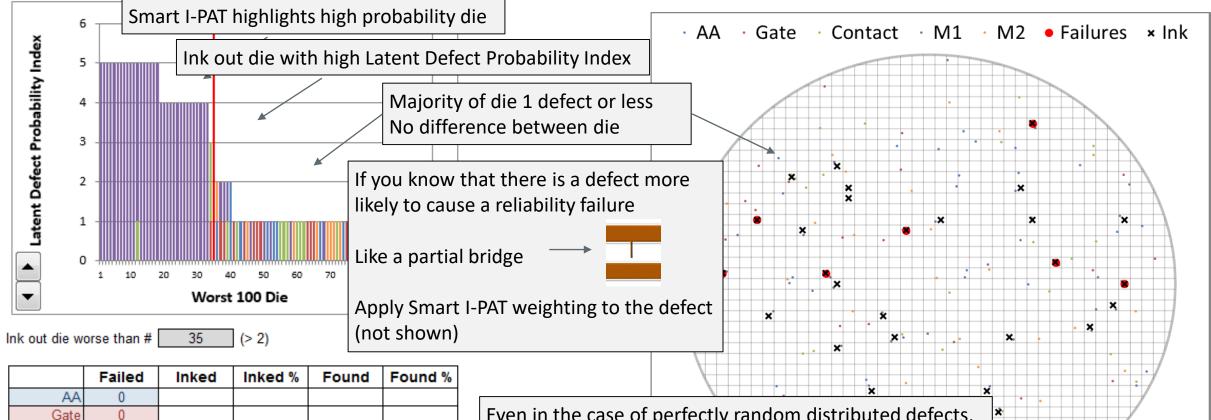

#### **Smart I-PAT**

#### Uses advanced correlation engines to weight defect probability based on defect attributes

# Smart I-PAT Random Distribution

Completely random distribution in defectivity

|  | Defects | AA   | Gate | Contact | M1   | M2   | Global                                                          | 7.00<br>49.00<br>1354<br>10 |

|--|---------|------|------|---------|------|------|-----------------------------------------------------------------|-----------------------------|

|  | Profile | Flat | Flat | Flat    | Flat | Flat | Die Size (mm)<br>Die Area (mm^2)<br>Die / Waf (est)<br>Failures |                             |

|  | Defects | 25   | 25   | 25      | 50   | 25   |                                                                 |                             |

Even in the case of perfectly random distributed defects, Smart I-PAT can help identify die more likely to have reliability failures

Contact

Stacked

Total

M1

M2

0

10

0

10

34

2.5%

(80.0%

8

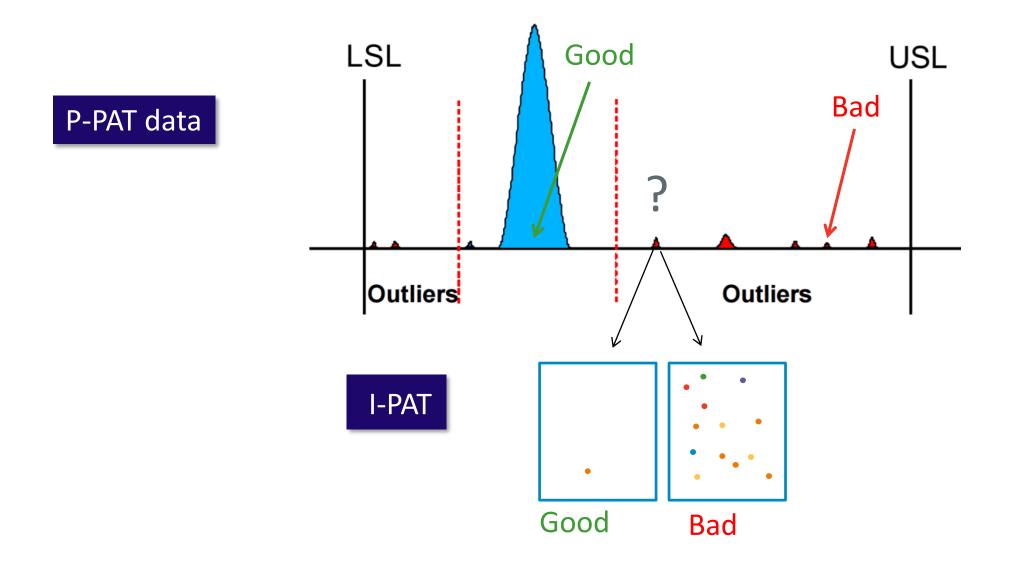

# Feed-Forward to Traditional P-PAT

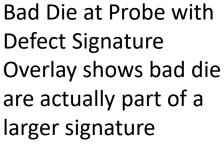

# Feed-Forward to Traditional G-PAT

Bad Die at Probe

KLA Tencor

#### Summary

- The defect types that impact reliability are generally the same as those that impact yield. They are distinguished primarily by size and proximity to critical design features.

- 2. Reducing overall defectivity is the best way to reduce the potential for latent reliability defects. However, die-level screening is becoming necessary to meet the new standards for reliability.

- 3. Part Average Testing methodologies are now being applied to inline defect data (e.g., "I-PAT") to improve capture of outlier die and reduce overkill from traditional PAT methods.

### References

- 1. D.W. Price and R.J. Rathert (KLA-Tencor Corp.). "Best Known Methods for Latent Reliability Defect Control in 90nm 14nm Semiconductor Fabs". Nineteenth Annual Automotive Electronics Reliability Workshop. Novi, Michigan. April 2017. <u>http://www.aecouncil.com/AECWorkshop.html</u>

- 2. Price, Sutherland and Rathert, "Process Watch: The (Automotive) Problem With Semiconductors," *Solid State Technology*, January 2018. http://electroiq.com/blog/2018/03/process-watch-baseline-yield-predicts-baseline-reliability/

- 3. D.W. Price and D.G. Sutherland, "Process Watch 7: The Most Expensive Defect, Part 2" Solid State Technology (on-line and print editions). July 2015. <u>http://electroiq.com/blog/2015/07/process-watch-the-most-expensive-defect-part-2/</u>

- 4. Shirley, Glenn and Johnson, Scott. "Defect Models of Yield and Reliability." Published lecture #13 for Quality and Reliability Engineering ECE 510 course at Portland State University, 2013. http://web.cecs.pdx.edu/~cgshirl/Quality%20and%20Reliability%20Engineering.htm

- 5. Siddiqui, Jeffrey et al, (DMEA) "On the Relationship between Semiconductor Manufacturing Volume, Yield, and Reliability", Microelectronics Reliability & Qualification Working Meeting. February 8, 2017

- 6. Roesch, Bill. "Reliability Experience." Published lecture #12 for Quality and Reliability Engineering ECE 510 at Portland State University, 2013. http://web.cecs.pdx.edu/~cgshirl/Quality%20and%20Reliability%20Engineering.htm

- Riordan et al. "Microprocessor Reliability Performance as a Function of Die Location for a .25um, Five Layer Metal CMOS Logic Process." 37<sup>th</sup> Annual International Reliability Physics Symposium Proceedings (1999): 1-11. DOI (<u>http://dx.doi.org/10.1109/RELPHY.1999.761584</u>).

- 8. Barnett et al. "Extending Integrated-Circuit Yield Models to Estimate Early-Life Reliability." IEEE Transactions on Reliability, Vol. 52, No. 3. (2003).

- 9. Kuper et al. "Relation between Yield and Reliability of Integrated Circuits: Experimental results and Application to Continuous Early Failure Rate Reduction Programs." *Proceedings of the International Reliability Physics Symposium* (1996): 17-21.

- 10. Automotive Electronics Council, Component Technical Committee, "Guidelines for Part Average Testing" AEC-Q001 Rev-D, December 9, 2011. http://www.aecouncil.com/Documents/AEC\_Q001\_Rev\_D.pdf

- 11. Price, D.W. and Rathert, R.J., "Methods and Systems for Inline Parts Average Testing and Latent Reliability Defect Detection." US Patent pending 15/480244